ZYBO-Z7-20でUbuntu 16.04 LTSを動かす(2) : FSBLとデバイスツリーの作成

ZYBO-Z7でUbuntu 16.04 LTSを動かす - メモ置き場

第2回目.

First-Stage-Boot-Loader(FSBL)の作成を行う.今回は最小限のPSの構成からFSBLをビルドしていこうと思う.必要に応じてカスタマイズしていく必要がある.

Zynqのブートシーケンスについてはこちらの記事が非常にわかりやすくまとまっている.

qiita.com

Vivadoでハードウェアを構成

Vivadoを使ってZynqで動かす回路を構成することから始める.Vivadoを立ち上げ,Create Block Designからブロックデザインを新規作成する.+ボタン(Add IP)を押してZynqのPSを追加する.追加したPSを図のように配線する.

IPをダブルクリックして,各種設定をしていく.

全体のブロック図.

I/O Peripheralの設定.

クロック周りの設定.ZYBO-Z7では33.333MHzにすること.

設定が完了したら,Sourceウィンドウのdesign_1を右クリックし,Create HDL Wrapperを選択,Let Vivado manage wrapper and auto-updateを選択しOKをクリック.すると勝手にHDLのラッパーが生成され,論理合成ができるようになる.Generate Bitstreamでbitstreamを生成する.bitstream生成が完了したら,File→Export→Export Hardwareでhdf(hardware description file)を出力する.bitstreamファイルはナントカ.runs/impl_1以下に,hdfはナントカ.sdk以下に生成される.

Xilinx SDKでFSBLをビルドする

VivadoからFile→Launch SDKを選択しXilinx SDKを立ち上げる.File→New→Application Projectを選択する.図のように設定しnext

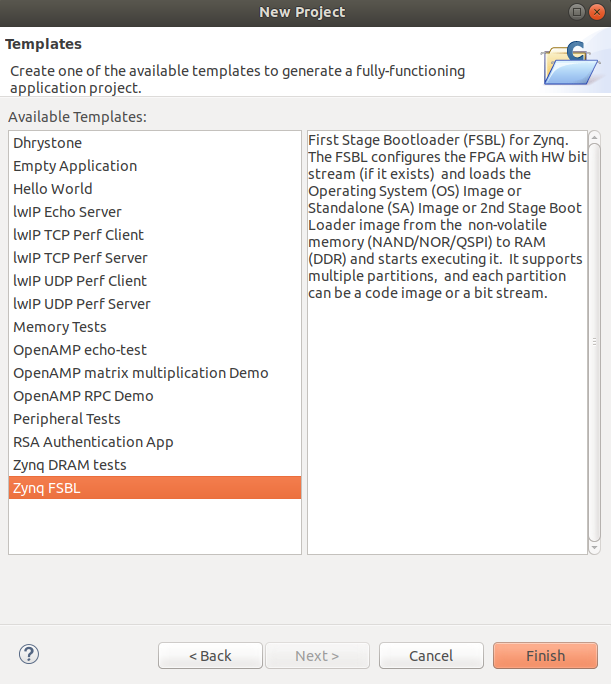

Available Templateの中にZynq FSBLという項目があるので,それを選択してFinishをクリック.

自動でビルドが実行されBinariesディレクトリにFSBL.elfが生成される.

デフォルトの設定ではFSBLを実行したときに何も表示してくれないので,下記サイトを参考にソースコードを少し変更する.

ZYNQのFSBLが動かない場合の対処法: なひたふJTAG日記

変更が終わったら再度ビルドをしておく.FSBL.elfはナントカ.sdk/FSBL/Debugにできる.

デバイスツリーの作成

blog 渓鉄: Xilinx SDKでDevice Treeを生成する

こちらの記事を参考にSDKからデバイスツリーを作成する.

Device Tree Generatorが必要なので,レポジトリから取ってくる.

git clone git://github.com/Xilinx/device-tree-xlnx.git

SDKのツールバーからXilinx→Repojitoriesをクリック.Local Repositoriesに上でダウンロードしたレポジトリを追加する.

SDKでNewからBoard Support Packageを開く.bootargsのvalueにconsole=ttyPS0, 115200, root=/dev/ram rw earlyprintkを追加してOKをクリック.自動でコンパイルがされてdtsが生成される.

生成されたsystem-top.dtsを以下に示す.

/*

* CAUTION: This file is automatically generated by Xilinx.

* Version:

* Today is: Mon Jan 28 21:47:57 2019

*/

/dts-v1/;

/include/ "zynq-7000.dtsi"

/include/ "pcw.dtsi"

/ {

chosen {

bootargs = "console=ttyPS0, 115200, root=/dev/ram rw earlyprintk earlycon";

stdout-path = "serial0:115200n8";

};

aliases {

ethernet0 = &gem0;

serial0 = &uart1;

spi0 = &qspi;

};

memory {

device_type = "memory";

reg = <0x0 0x40000000>;

};

};